Fall IDF 2005 - Day 1: Intel's New Architecture Details Revealed

by Anand Lal Shimpi on August 23, 2005 1:17 PM EST- Posted in

- Trade Shows

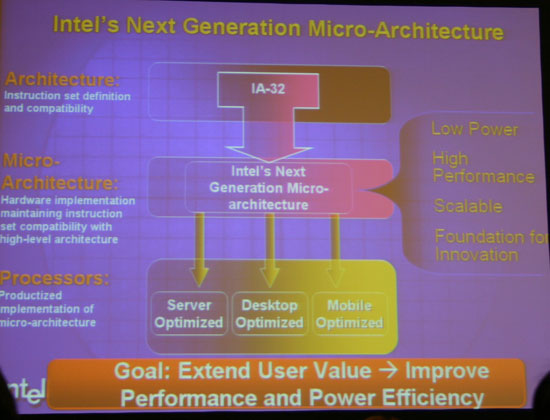

Immediately following the slightly disappointing keynote, Intel revealed a few more details about their next-generation microprocessor architecture. As of now, the new architecture doesn't have a name, but we've got some of its features now.

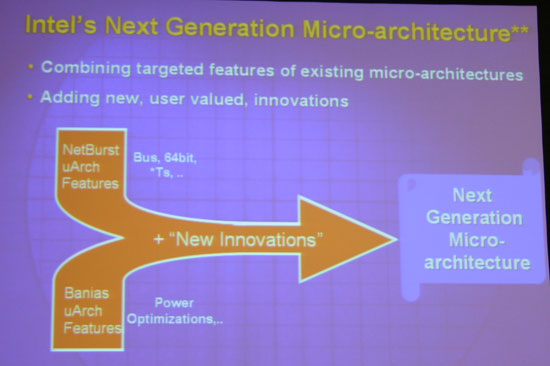

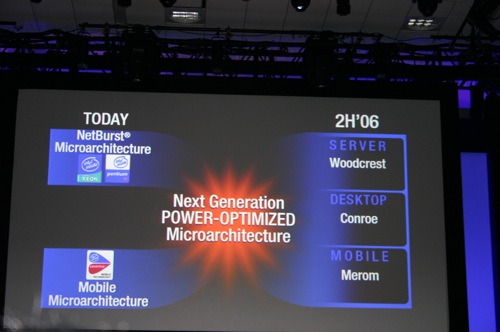

Intel has come out and said that the next-gen microarchitecture will be a unified architecture, combining the lessons learned from the Pentium 4's NetBurst and Pentium M's Banias architectures. To put it bluntly, the next-generation microprocessor architecture borrows the FSB and 64-bit capabilities of NetBurst and combines it with the power saving features of the Pentium M platform. Features like virtualization and security will also be a part of the new architecture.

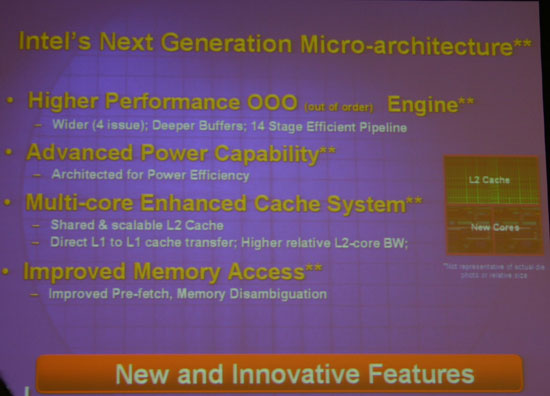

Contrary to wild speculation, Intel's new architecture will continue to feature an Out of Order execution core; a direct descendant of the Pentium M and Pentium 4 predecessors. The core will be a wider 4-issue core (4-issue decode, execute and retire) with deeper buffers, presumably with more instructions in flight than the Pentium 4 courtesy of the 4-issue core.

The basic integer pipeline appears to be 14 stages long, making it a significant decrease from the 31+ stage pipeline in Prescott and a slight increase from the 12 stage pipeline in the Athlon 64. Intel's move to a much shorter pipeline will definitely decrease power consumption (as well as clock speed), but hopefully improve performance considerably.

Note that with a 4-issue core, the new processors will actually have a higher degree of ILP than AMD's Athlon 64, and with a slightly deeper pipeline the CPU should be able to reach higher clock speeds than what AMD has been able to achieve. We'd expect that at 65nm these new cores could run as high as 3GHz in clock speed, but definitely not at the 4GHz+ levels that we currently have with the Pentium 4.

Given the significant reduction in pipeline stages, Intel's claims of a 5x improvement in performance per watt over the Pentium 4 architecture seems very realistic.

The new architecture will feature a shared L2 cache between the cores, much like what we've seen from Yonah already. Intel also said that there would be a higher "relative" increase in L2 cache bandwidth. The new processors will also apparently feature a direct L1-to-L1 cache transfer system in order to improve the currently very poor cache-to-cache transfer performance of Intel's dual core processors.

There are also a number of new prefetching algorithms, allowing data to be prefetched from L1 to L1 (one core to another), L1 to L2, etc... Intel is also introducing speculative data loads with the new architecture, loads to be executed ahead of stores if a dependency is predicted to not exist between the two. We are waiting for more details on the feature to be exact about its functionality.

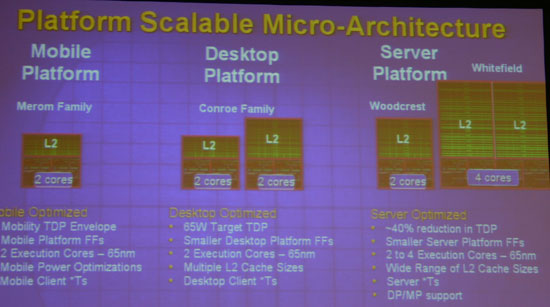

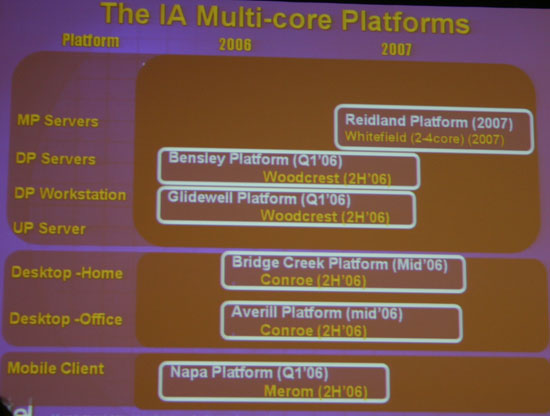

Both Conroe and Merom (desktop and mobile) will feature 2 cores. Intel says that Conroe will be available in multiple L2 cache sizes, while Merom will not. We'd assume that the multiple L2 cache sizes would be to accomodate and differentiate products like the Extreme Edition.

On the server side, the first next-gen architecture CPU will be the dual core Woodcrest, followed by the quad-core Whitefield processor.

More info as we get it.

26 Comments

View All Comments

knitecrow - Tuesday, August 23, 2005 - link

An extremely predictable direction; I actually yawned in the middle ... maybe because its time for my coffee or maybe the details do not excite.All-round very boring.

I wanted to see a new architecture that can dazzle.

- a proper vector co-processor similar to what PPC970FX or the Xbox360 XPU have.

- hyperthreading done proper – like what IBM does with the Power5 series

- on-die memory / PCI-e controller

***YAWN****

I want to see what AMDs next gen architecture will offer. They seem to more on the cutting edge.

erinlegault - Tuesday, August 23, 2005 - link

Quad-core? Who's going to be the first out with that?Den - Tuesday, August 23, 2005 - link

IBM's had a quad core Power 5 out for a while now...If you mean in the x86 world though, yes, that will be an interesting race.

Furen - Tuesday, August 23, 2005 - link

Well AMD can already produce quad cores since the SRI on current a64s actually has 4 ports for cores. If you mean who will be first to market I'd guess AMD as long as they can pull off a timely 65nm shrink... it always comes back to that.ViRGE - Tuesday, August 23, 2005 - link

Considering how long it has taken AMD to get in to the swing of 90nm process, I would be very surprised if they beat Intel to 65nm. Intel has the size and the money to make ridiculous investments in new process technologies, and I think that will be enough to keep them ahead, in spite of the AMD/IBM partnership.Furen - Tuesday, August 23, 2005 - link

LOL, contrary to wild speculation? That articles was one of Nicholas Blachford's saner predictions. I mean, it's more down to earth than his anti-graviton engine for faster-than-ligth travel or his "the Cell will redefine the chip industry" garbage.