Spring IDF 2006: Introducing Intel's new Core processors

by Anand Lal Shimpi on March 7, 2006 12:06 PM EST- Posted in

- Trade Shows

Conroe, Merom and Woodcrest - General Performance Expectations

While we'll get a better idea of performance of Conroe, Merom and Woodcrest later today, Rattner did share some high level numbers:

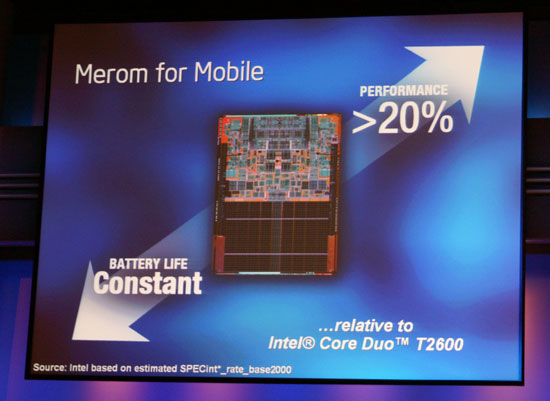

Merom offers 20% higher performance at a constant battery life compared to the Core Duo T2600.

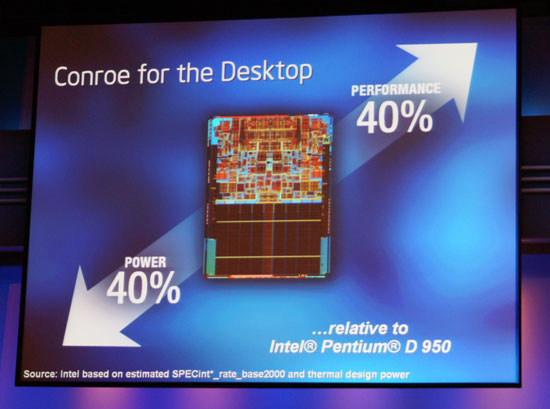

Conroe offers a 40% increase in performance with a 40% decrease in power compared to the Pentium D 950.

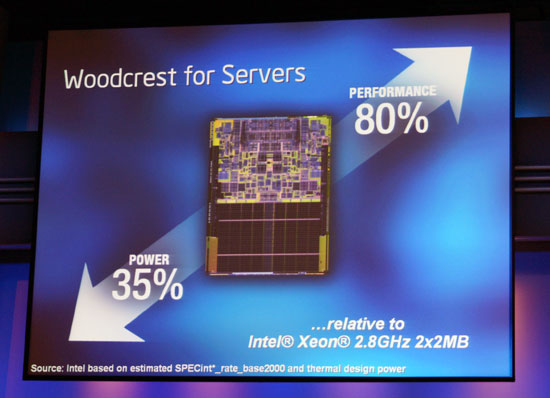

Woodcrest sees an 80% increase in performance and a 35% decrease in power compared to a Xeon 2.8GHz with two 2MB caches.

Obviously we've got no clue under what circumstances these figures were measured, but the numbers are exciting nonetheless.

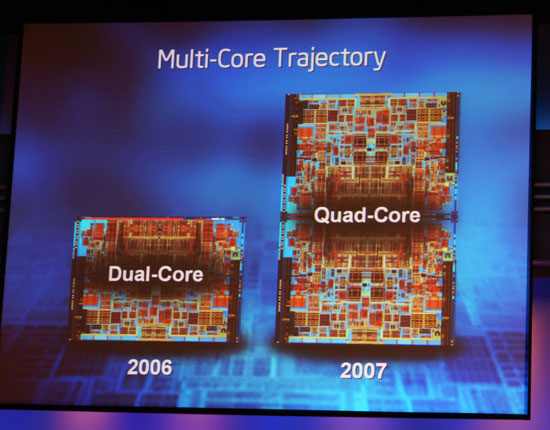

Both AMD and Intel have announced that they would have quad-core processors in 2007, however Rattner mentioned that there's no reason to expect 8-core processors in 2008 but rather further improvements on the ILP level to each one of those 2 or 4 cores.

The final focus on energy in Rattner's keynote was about the platform. Although currently the power consumption balance between the CPU and the rest of the platform (chipset, memory, display) is about 50/50, with the new Core processors only about 1/3 of the total system power consumption ends up being used by the CPU - meaning that platform power consumption now ends up being a limiting factor.

Pat Gelsinger's keynote has just begun, we'll be reporting on that next...

15 Comments

View All Comments

nicolasb - Wednesday, March 8, 2006 - link

What do I need to do so that anandtech.com will let me see the pictures when I'm reading its articles? :-(stephenbrooks - Sunday, March 12, 2006 - link

I've found that the pictures load as 1x1 blank GIFs in Opera but appear fine in IE. That really sucks.zephyrprime - Tuesday, March 7, 2006 - link

Anand says that SSE will execute in a single cycle but I think Intel really meant that SSE will have single cycle throughput, not latency. Notice that in the slide Intel simply writes "single cycle SSE". SSE instructions (except some of the really easy ones) are currently broken down from 128bits -> 2x64bit instructions to actually execute. This has long been the biggest weak point of SSE.I expect latency to be 5cycles for SSE FP multiply (it's currently 6). I expect throughput to be 1 cycle for SSE FP multiply (it's currently 2). So instruction throughput will theoretically double.

Anand Lal Shimpi - Tuesday, March 7, 2006 - link

You are quite correct, Intel just clarified this point to us and I've updated the article. Thanks for the pointer :)Take care,

Anand

Hulk - Tuesday, March 7, 2006 - link

Do all SSE instructions execute in the same number of cycles?This crazy projections are always more exciting when they come from Intel because they do have a track record of NOT producing vaporware.

On the other hand their performance figures are always way optimistic.

If you look at the middle ground Conroe will probably be a bit faster than X2 per clock cycle. We'll see if they can ramp up the clockspeeds for release...

Doormat - Tuesday, March 7, 2006 - link

"While we'll get a better idea of performance of Conroe, Merom and Woodcrest later today, Rattner did whet our appetites"Is that a typo or a reference (inside joke?) about performance numbers....

Rock Hydra - Tuesday, March 7, 2006 - link

That's the proper use for the word.I suppose what he's trying to say is they're satisfied with the info disclosed at the time.

xtremejack - Tuesday, March 7, 2006 - link

Whet means sharpen, right. Means becoming eager for more information, I supposeadamfilipo - Tuesday, March 7, 2006 - link

same here. images arent loadinghope conroe kicks ass, my next powermac will have it

DigitalFreak - Tuesday, March 7, 2006 - link

show me the benchies!