Intel Developer Forum 2007 - Day 1: Nehalem, Intel's GPUs, 32nm and More

by Anand Lal Shimpi on September 18, 2007 1:17 PM EST- Posted in

- Trade Shows

The Integrated Graphics Revolution

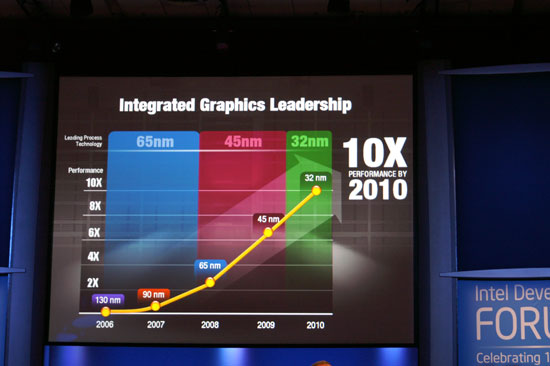

With the pending collision course between the CPU and the GPU, Intel confirmed that it would begin manufacturing its integrated graphics cores on smaller manufacturing processes moving forward.

During the second half of Intel's 45nm era, Intel will bring the GPU on-die and plans to improve graphics performance significantly over where we're at today. The improvement is necessary in order to remain competitive with AMD's Fusion processors. From this point on, all integrated graphics will be on the microprocessor die.

By 2010, the first from-scratch CPU and GPU from Intel to be designed for 32nm will converge and we'll see a significant improvement in entry-level graphics performance.

23 Comments

View All Comments

strikeback03 - Thursday, September 20, 2007 - link

Which temperature units is that "160 below 0" in?amdsupport - Tuesday, September 18, 2007 - link

Did Sears/Kmart design part of the chip also? :p

seems like intel could come up with a more creative name than that.

I'm kinda curious though what consumer electronics will end up with some form of this.

cheburashka - Tuesday, September 18, 2007 - link

The believe the codename is actually Canemore.AmberClad - Tuesday, September 18, 2007 - link

I did a double take when I saw that too. I couldn't believe the PR people let that one through. This is what happens when you randomly pick the name of a city, without considering the alternate connotations of that name.strikeback03 - Thursday, September 20, 2007 - link

I was wondering if it was intended as a joke that an architecture designed for the CE market is given the same name as a CE company.JarredWalton - Tuesday, September 18, 2007 - link

Code names are not product names. They could call something "AMD- Thunderbird" internally if they wanted; it's only the final product names that really matter in terms of trademarks.bespoke - Wednesday, September 19, 2007 - link

In the mid nineties, Apple got in trouble for a product with a code name of "Sagan". Carl Sagan's lawyers made a stink about Apple's use of his name, even thought it was an internal code name. Apple engineers changed the code name to "BHA", which was understood to mean "butt-head astronomer". Sagan sued for libel after that. :)archcommus - Tuesday, September 18, 2007 - link

Looks like current trends will continue for the near future. Both AMD and Intel are heading in similar directions: new architecture on 65 nm, same architecture on 45 nm, and then a brand new architecture that is highly parallel and a large divergence from CPU designs of today. And, just like today, it appears Intel will get to that new architecture at least a half year if not a full year ahead of AMD. Glad to see things accelerating so quickly in the CPU market, as long as AMD DOES keep catching up we should be okay!Question: Does having a FSB implementation versus an on-die memory controller have any tangible advantage or disadvantage to the end user besides the impact on memory performance? Which types of applications see this impact the most? It's surprising that I've owned an Athlon 64 for over two years now, and if I upgraded any time before next summer, I'd STILL be going "backwards" regarding that. Wonder why Intel stuck with it for so long.

Lord Banshee - Tuesday, September 18, 2007 - link

I would say you will not see a difference in Mem Performance going from A64->Core2Duo. But if intel does do the IMC then it might allow them to have smaller caches with less performance hit then makes their CPUs cheaper or have more room for other random logic.Shadowmage - Tuesday, September 18, 2007 - link

Nehalem is definitely NOT 8 cores on a single die. Nehalem is 4 cores on a single die, with possibility for MCP solutions (8 cores on 2 dies).