Intel Developer Forum Spring 2004 - Day 2: Roadmap Updates

by Derek Wilson on February 19, 2004 12:47 PM EST- Posted in

- Trade Shows

The day two keynote wasn't quite as eventful as the keynote of Tuesday. Basically, Mike Fister, Bill Siu, and Anand Chandrasekher brought us up to speed on all the developing technologies and initiatives emphasized last Fall. The phrases we heard most often in the keynote were very similar to "as we indicated last IDF." We heard about Vanderpoolagain, this time with the corporate environment being emphasized rather than home use. La Grande was mentioned again as an important factor in future secure computing, but nothing really new was introduced. The possible downsides of the technology still haven't been addressed, but all this stuff is still very much in its infancy and is likely to evolve a great deal before anything solid comes about.

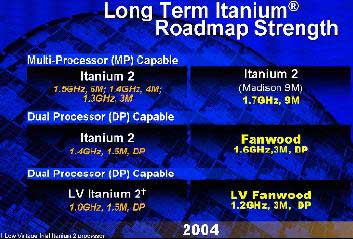

Of course, roadmaps were updated. We have been filled in on the holes that were left by the introduction of 64bit extensions, and Mike Fister gave us the code names of the dual processing and low voltage IA-64 processors in development, as well as the Bayshore (PCIe and DDR2) platform for Itanium processors. There was also mention of visualization technology Silvervale, and reliability hardware Pellston of we know exactly as much as this sentence conveys. Fully buffered DDR2 DIMMs are also being placed on the map for enterprise platforms as well.

Dothan is apparently ready for a "quick ramp" according to Anand, while we can expect the Sonoma mobile platform to be available in the second half of the year bringing all its enhancements to Centrino.

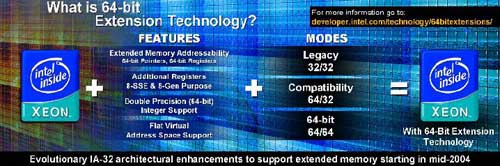

We got another look at a rundown of the 64bit extensions Intel has implemented in the Prescott and Nocona cores which looks very much like it could have been a slide from AMD a few years back.

7 Comments

View All Comments

TrogdorJW - Friday, February 20, 2004 - link

Actually, a single-channel memory bus is 64-bits wide, and a dual-channel is 128-bits. DDR200 which is equivalent to 400 MHz transfers 3.2 GB/s of data. 3200 MBps / 400 MHz = 8 bytes, which is 64-bits.Technically, you could create 256-bit channels like they do on graphics cards, but with the trace lengths on motherboards, it's expensive and difficult to pull off. In fact, I remember one server motherboard manufacturer making a 128-bit SDRAM implementation of a P3 Xeon chipset. Back in those days, it was a pretty big deal, as it allowed you to use PC133 SDRAM and get the same performance as DDR266. Actually, performance was even faster as CL2 PC133 was available, whereas DDR266 was only available in CL2.5 at the time. It cost a lot, though: $450 or something just for the motherboard, although it was dual-proc.

Pumpkinierre - Thursday, February 19, 2004 - link

I was talking about the same thing on another post, trog #3, and someone else said that the pentium already had a 64bit wide data bus. So you wouldnt even have to double up. The extra memory on the address bus is going to be missing but you dont need that now. Really 64 bit is totally internal with the extra registers etc. so as you say a BIOS upgrade or rewrite should do it even on Sckt 478 mobo.GonzoDaGr8 - Thursday, February 19, 2004 - link

I thought that the extra pins for A64 were for the dual-channel memory.XPgeek - Thursday, February 19, 2004 - link

i was thinkig that the extra pins on the A64's were for increased power delivery...TrogdorJW - Thursday, February 19, 2004 - link

Simple, Jeff: Like they did with the 386SX, which was a 32-bit processor core on a 16-bit memory bus. In that case, when you needed to access a 32-bit instruction, address, etc. you had to get it in two pieces.Really, though, AMD64/IA32e do not have as many 64-bit accesses as you might imagine. Instructions are still 32-bits, and most integers will be 32-bit. Pointers might be 64-bit (not positive), but since FP / MMX / SSE / SSE2 / SSE3 are all 64-bit or 128-bit, I think it would be quite simple (relatively speaking) to have a 64-bit processor run on the current motherboards. The biggest problem would be getting the motherboard BIOS to understand the New World Order, which would require a BIOS update at the very least, I think.

Jeff7181 - Thursday, February 19, 2004 - link

I'd be amazed if enabling 64-bit extensions didn't require a new socket (socket 775). If I'm not mistaken, isn't the increased pincount of socket 754 for the extra memory address bus width? And the added pincount of socket 940 due to the extra HT links? Why would it be any different for Intel? If they're using 478 pins right now, how could they increase the size of the memory bus without adding more pins?Pumpkinierre - Thursday, February 19, 2004 - link

You're on the right track, happy digging!