Intel Broadens FPGA Range with New Products Across All Six FPGA Platforms

by Anton Shilov on September 15, 2023 4:30 PM EST

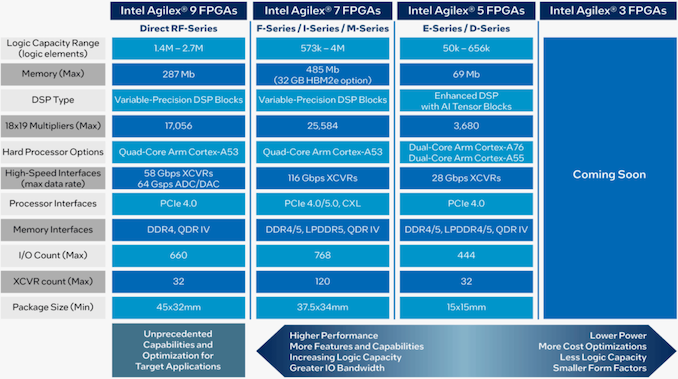

Intel's Programmable Solutions Group (PSG) is broadening its FPGA product range with the introduction of six new programmable platforms aimed at different types of customers and workloads. In addition to a new sub-family of Agilex 5-series offerings, Intel is launching its all-new Agilex 3 series offerings along with new Agilex.

The highlight of today's announcement is the Intel Agilex 3 FPGA series of power and cost-optimized FPGAs in compact form factors. The family includes the Agilex 3 B-series FPGAs that boast a higher I/O density in compact form factors (compared to Intel Max 10 FPGAs) and are optimized for board and system management, including server platform management applications.

On the other side of the Agilex 3 spectrum is the C-series FPGAs that are engineered to provide supplementary capabilities, making them apt for a broad spectrum of complex programmable logic devices (CPLD) and FPGA applications across various industries. Intel says that its Agilex 3-series FPGAs will be available soon without disclosing when exactly.

Another noteworthy introduction is the Intel Agilex 5 FPGA E-series based on the 2nd Generation Hyperflex FPGA architecture and tailored for embedded edge applications and therefore featuring high performance efficiency. Intel produces these FPGAs in house using its Intel 7 manufacturing technology (formerly known as 10 nm Enhanced SuperFin), which is why it says that these parts deliver 1.6 times higher performance per watt compared to competing FPGAs made on a 16 nm-class process technology (possibly referring to Xilinx's FPGAs built in this process node). Additionally, this FPGA series integrates an AI tensor block, a feature previously exclusive to Intel's premium programmable parts, positioning it as a solution for edge AI tasks. Intel will start sampling Agilex 5 E-series parts with design software in Q1 2024. A system simulator for these FPGAs will be available in the cloud in late 2024.

Intel also said that it had begun shipments of its Intel Agilex 7 FPGAs with the R-Tile chiplet. These FPGAs offer a PCIe 5.0 interface with the CXL protocol on top that allow to quickly deploy programmable accelerators for specific tasks that can benefit from higher bandwidth and lower latencies.

In addition to revealing new FPGAs, Intel also said that the first commercial product based on its F2000X infrastructure processing unit platform is now shipping. The part is the Napatech F2070X IPU that has two 100 GbE ports and is powered by the Agilex AGFC023 FPGA and an Intel Xeon D SoC.

Rounding off the new introductions is the Nios V/c compact microcontroller, which is a soft-core IP, based on the RISC-V architecture, which can be programmed using the company's Quartus Prime Pro software.

Source: Intel

3 Comments

View All Comments

Unashamed_unoriginal_username_x86 - Saturday, September 16, 2023 - link

Agilex 9 seems a bit confusing having lower throughput than Agilex 7, anyone know why that is? From what I could find it's largely used for military RF applications, so maybe it hasn't been refreshed yet bc longer TTM, mature processes for analog and whatnot?erinadreno - Monday, September 18, 2023 - link

The 64Gsps ADC/DAC are actually very impressive and massive. If you need software defined radio then it's pretty hard to do a discrete version of agilex 9. It comes after the agilex 7. Making a large but simple chip isn't that hard. But making a smaller but more complex chip is more difficultflgt - Tuesday, September 19, 2023 - link

MAX10 has some really nice SOC features that aid in system integration (integrated Flash memory for CPLD startup emulation, single power supply operation, etc.). It will be interesting if Agilex 3 incorporates any of these features or if it will just be a standard cut down FPGA.