IDF Fall 2006 - Day 2: Geneseo, Santa Rosa, Memory Roadmap and More

by Anand Lal Shimpi on September 28, 2006 3:43 AM EST- Posted in

- Trade Shows

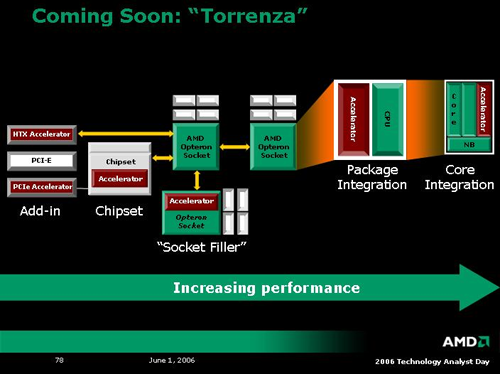

Earlier today during Pat Gelsinger's Keynote, Intel announced its work with IBM to develop the successor to PCI Express, codenamed Geneseo. We likened Geneseo to AMD's Torrenza initiative, and were able to get some more background information on Geneseo and how it is likely to be implemented once it makes its debut.

Intel is in a precarious situation; since there is a demand for a higher bandwidth, lower latency interconnect than PCI Express, AMD's Torrenza platform makes a lot of sense for 3rd party solution and accelerator vendors. Those vendors would be able to gain access to a high bandwidth, low latency interconnect by utilizing coherent Hyper Transport and plugging directly into an Opteron socket or via HTX slots on a motherboard. With no competing standard from Intel and AMD being an easy company to work with, momentum for AMD's Torrenza platform was growing in anticipation of its eventual implementation.

AMD's Torrenza Platform

From Intel's standpoint, simply releasing a competitor to Hyper Transport wouldn't make a lot of sense since it would simply further divide the market. Instead, Intel and IBM got together and proposed an extension to PCI Express that would offer both higher bandwidth and lower latency. Since PCI Express is already an industry standard embraced by all sorts of manufacturers, the evolutionary move to another PCI Express based interface makes a lot of sense and is more likely to gain traction than requiring vendors to produce HTX compatible solutions.

Although the spec is not yet defined, Geneseo (pronounced jen-eh-see-oh) PCI Express will be a backwards/forwards compatible interface, simplifying migration. Transfer rates will be on par with PCI Express 2.0, at 5 GT/s per lane, doubling the bandwidth of current PCI Express.

Geneseo is designed to tackle all of the sorts of add in "accelerators", whether they are GPU or physics, as long as they don't need cache coherent communication with the host CPU. If they do need full cache coherency, then Geneseo falls short however Intel's announcement that it would be offering FSB bus licenses to companies like Xilinx that are interested in a cache coherent interface picks up where Geneseo left off.

Basically Intel's interconnect solution is two fold:

1) If you don't need a cache coherent interface, then Geneseo will work just fine. It will be an industry standard specification, built upon PCI Express that will undoubtedly have broad industry support much like PCI Express does today.

2) If you do need a cache coherent interface, for example if you're building an accelerator that does need to work very closely with the CPU, then you'll have to license Intel's FSB for use in Intel systems, or design a coherent Hyper Transport interface for use in AMD systems.

More than likely what will happen is that once Geneseo gains traction the majority of accelerators, those that don't need to remain near the CPU, will transition to a Geneseo interface since you only need to build one accelerator that can work on both AMD and Intel platforms (assuming AMD offers Geneseo support, which since it supports PCIe we can't see AMD not supporting Geneseo). In the cases where you're building an accelerator that must reside next to the processor, then you'll have to build a platform specific device, e.g. something that implements Hyper Transport for AMD or something that utilizes Intel's FSB license for Intel platforms.

Assuming that the eventual specifications of Geneseo are competitive with what AMD can offer with HTX slots in its Torrenza platform, then we do see a lot of promise with Geneseo. We would still like to see Intel ditch its aging FSB architecture, but it appears that the process of following in AMD's footsteps is a slow one.

7 Comments

View All Comments

porkster - Thursday, September 28, 2006 - link

If you ask me, laptop graphics is a major issue at the moment.Intel really needs to bring forth the Santa Rosa chipset to set a new bench level for gfx. x3000 maybe just enough to move upto, but even the power of the gfx intergrations, isn't that great.

Vista will make most laptop's second generation, the day it is released.

johnsonx - Thursday, September 28, 2006 - link

It's been speculated that AMD would have something to show in a hotel room across the street from IDF as they have in past years. So far it seems AMD is silent this year. A bad sign? AMD not as close on quad-core and/or K8-L as everyone has been hoping?What's the industry scuttlebutt on this?

smitty3268 - Thursday, September 28, 2006 - link

I was wondering the same thing. Perhaps K8L won't actually be any faster than current Conroes?fitten - Thursday, September 28, 2006 - link

You know... as much as people say this, it's odd that the aging FSB architecture is in the fastest system on the market right now... even faster than "newer" non-FSB architecture. Sure, it may not post as high synthetic benchmark bandwidth and latency numbers but when running applications, it sure seems to do pretty well. Sure, a new interconnect architecture might make it even faster and cooler but simply because the FSB is "aging" doesn't necessarily imply that it doesn't work.

Xenoterranos - Thursday, September 28, 2006 - link

While I agree with your point, at the crux of the argument is the question about when FSB will be too out dated. We all know it doesn't scale that well, and it's a testament to Intel's engineering teams that they are able to make it work so well. On the Xeons we see them moving toward dual FSB's, considering that we now have dual core processors, maybe this isn't that bad of a sign for the good ol FSB. HyperTransport is making great strides, and I would love to see Intel direct some of it's considerable brainpower at (co?)developing a new system like that instead of finessing all the power they can out of the one they have. I think they really believe that FSB is the way to go right now, but I would seriously doubt they have no plans to move to something like HT in the future.fitten - Friday, September 29, 2006 - link

Intel's serial interconnect that they're working on is called CSI.Clauzii - Thursday, September 28, 2006 - link

I find it kind of funny to see Vista running on MAC OS ;)