Intel Developer Forum Fall 2002 – Day 2: More on Hyper-Threading

by Anand Lal Shimpi on September 10, 2002 9:23 PM EST- Posted in

- Trade Shows

This article first appeared on the AnandTech Newsletter. Click Here to Subscribe.

We just finished up a meeting with Bill Siu, VP and General Manager of Intel’s Desktop Platforms Group and he gave us some updated information on everything from Banias to Hyper-Threading.

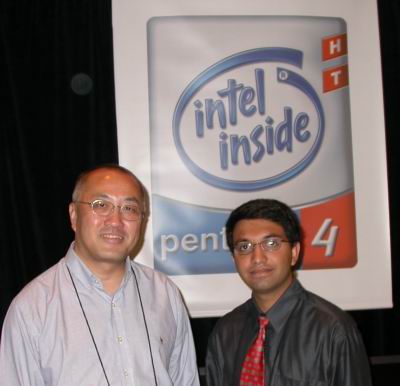

Before we get to Bill we have to introduce you to a person that you’ve probably read a lot about online:

I ran into Johan de Gelas of Ace’s Hardware, one of the most well respected and technical websites in our community.

Johan of Ace's Hardware

As always it was a pleasure talking to Johan as well as Brian Neal, a news editor for Ace’s.

Anna of x-bit labs

I was also graced by the presence of Anna Filatova, of x-bit labs while preparing this piece.

Our talk with Bill Siu was entertaining as always, but it was definitely short and to the point. The most interesting tidbit we gained from the conversation was in regards to performance with Hyper-Threading. Apparently there have been a number of revisions to the Hyper-Threading cores since we first looked at its performance with the Xeon months ago. These updates have apparently improved performance of Hyper-Threading to the point where we might see some performance gains in situations where we saw the opposite originally.

Bill Siu and I beneath the new Pentium 4 with Hyper-Threading logo

We asked Bill why Intel was waiting until the middle of next year to introduce Springdale, their first Dual Channel DDR chipset for the Pentium 4; his response was that the 850E is doing just fine and it won’t be until the middle of next year that the cost structure of Springdale will make sense to introduce.

Bill also told us that Banias’ FSB borrowed a lot of what Intel learned with the NetBurst FSB while the general architecture is Pentium III derived with a larger cache and a lot of microarchitectural enhancements. This confirms what we originally speculated about Banias, making the case even stronger for a P3 derived core (with features such as Micro-Ops Fusion, etc…) with a 1MB L2 cache as we reported earlier today. This also leads us to believe that a 400MHz FSB isn’t out of the question for Banias either.

We fished for some more Prescott info but we came up empty handed for the most part, maybe later ;)

0 Comments

View All Comments